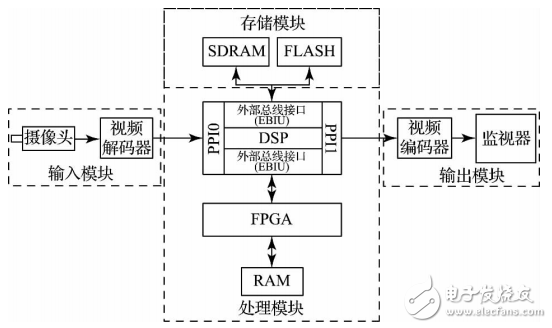

The application of real-time video image processing technology is very extensive. There are robot vision, resource detection and medical image analysis in the civilian field. In the military field, there are missile precision guidance, enemy target reconnaissance and tracking. The hardware structure of DSP+FPGA is adopted in this design. DSP uses ADI's high-performance dual-core DSP-BF561 as the main processor, which is responsible for the scheduling and data flow control of the whole algorithm, and completes the collection and display of image data and the core algorithm. The FPGA, as the coprocessor of the DSP, relies on its high parallel processing capability to complete a large number of cumulative multiplication operations in image preprocessing. The two cores of the DSP communicate with the FPGA through interrupts, so that the processors of the system work in parallel, which improves the utilization efficiency of the DSP core and the FPGA, and ensures the real-time performance of the system acquisition and display. The image acquisition and processing system mainly includes four modules: an image acquisition module, a storage module, a processing module, and a display module. Figure 1 shows the block diagram of the hardware structure of the image acquisition and processing system of DSP+FPGA. Figure 1 Image acquisition and processing system hardware structure The front-end input module of the system is realized by a CCD camera and a video decoder 7181B. The video decoder converts the analog video signal received by the CCD into a standard YUV 4:2:2 digital video format with an image size of 720 & TImes; 576. The converted image data is first stored in the RAM through the dedicated video interface PPI0 of the ADSP-BF561. When the image data of one frame is captured, the DMA of the DSP is interrupted. At this time, the FPGA first performs image preprocessing on the acquired image data. Then the DSP retrieves the preprocessed data and completes the corresponding image processing algorithm. Finally, the processed video data is sent to the video encoder 7171 by the DMA controller through the PPI1 interface, and converted into a standard analog PAL video signal to the monitor. display. The role of FLASH is to store the program running on the system and boot the system. For system requirements, DSP uses Analog Devices' ADSP-BF561 processor, a 16-bit fixed-point DSP for multimedia and communications applications that integrates two Blackfin processor cores, each capable of 600MHz continuous jobs. The FPGA uses Altera's EP2C5, which has 4,608 logic cells, 13 18 & TImes; 18 hardware multipliers, and up to 142 user-defined IO ports. The CCD camera captures the standard PAL analog video. The design uses ADI's ADV7181B video decoder chip to perform A/D conversion on the analog signal. The ADV7181B is a widely used video decoder chip from Analog. The chip can automatically detect the input composite video signal, and configure the interface through the I2C bus to select the image output format. Since the black and white image has been able to meet the detection needs of the system, the analog signal is output in the ITU-R-656 format YUV (4:2:2). The Y signal is a luminance signal, and the U and V signals are chrominance signals. This makes it possible to extract the luminance signal of the format directly, which is much simpler than converting to the traditional RGB format. Copper Tube Terminals Without Checking Hole Our company specializes in the production and sales of all kinds of terminals, copper terminals, nose wire ears, cold pressed terminals, copper joints, but also according to customer requirements for customization and production, our raw materials are produced and sold by ourselves, we have their own raw materials processing plant, high purity T2 copper, quality and quantity, come to me to order it! Copper Tube Terminals Without Checking Hole,Cable Lugs Insulating Crimp Terminal,Cable Connector Tinned Copper Ring Terminal,Tubular Cable Lugs Crimp Terminal Taixing Longyi Terminals Co.,Ltd. , https://www.longyicopperlugs.com

Design and Implementation of a DSP+FPGA Video Image Acquisition and Processing System

1 Introduction