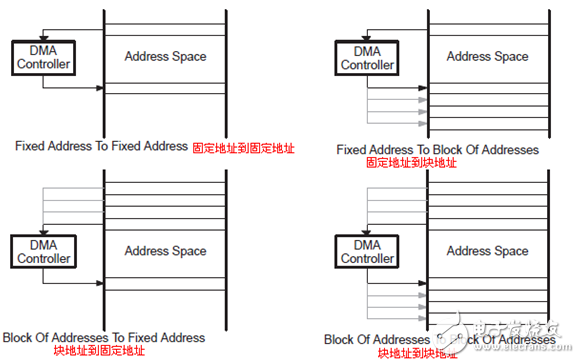

DMA is the acronym for Direct Memory Access. On the bus of the CPU, there will be more memory at the same time. If you want to copy the contents of the memory 1 to the memory 2, if you don't use DMA, you have to go directly to the CPU. The operation process is roughly: the CPU is ready for the memory 1 The address and control signals, read the contents of the memory 1, store them in the internal registers of the CPU, prepare the address and control signals of the memory 2, and write the contents of the registers to the memory 2. If it is a single data operation, this process is necessary, and the efficiency problem is not obvious, but if you want to copy a large amount of data at a time (such as one frame of image data, a batch of voice data, etc.), then loop a data and a data by the CPU. The operation is not only slow (due to the architecture design, the CPU usually does not access the external bus very fast), but also causes the CPU and bus to be occupied at all times, and the efficiency is very low. If you do a hardware controller inside the CPU, which is responsible for this data movement operation (automatic generation of memory address and control signals, automatic read and write timing), not only can the speed be much improved, but the CPU can also do other things during this period. So the efficiency will be much higher. DMA means that there must be a DMA controller on the hardware to do this. Now the concept and role of DMA has been greatly extended. Many complex CPUs even contain many DMA controllers. DMA operations are no longer limited to external memory, internal memory, internal and external memory, and various standards. Between the peripherals and the memory, there is a DMA controller to implement data exchange, so that the functions of the CPU are getting stronger and stronger, and the data processing is getting faster and faster. The MSP430F15X/16X family of microcontrollers has a DMA controller that guarantees high-speed data transfer. For example, the contents of the ADC conversion memory can be directly transferred to the RAM unit by the DMA controller. MSP430 series MCU extended DMA has all the peripheral triggers, which can provide advanced configurable data transmission capability without CPU intervention, thus speeding up MCU-based signal processing process, DMA transmission trigger source to CPU It is completely transparent, and the DMA controller provides precise transfer control between the memory and external and external hardware. DMA eliminates data transfer latency and various overheads, freeing up the RISC CPU so that it spends more time processing data than on the task being processed. The DMA module of MSP430F16x series MCU has the following characteristics: Data transfer does not require CPU intervention, and is completely managed by the DMA controller. Transmitting data over the entire address space, block mode transmission up to 65536 bytes; can improve on-chip peripheral data throughput, achieve high-speed transmission, only need 2 MCLK for each word or byte transfer; reduce system power consumption, Even when the on-chip peripherals perform data input or output, the CPU can be in ultra-low power mode without waking up; byte and word data can be mixed: DMA transfers can be byte-to-byte, word-to-word, word Section to word or word to byte. When word-to-byte transfers, only the lower byte of the word can be transferred. When transferring from byte to word, it is transferred to the low byte of the word, and the high byte is automatically cleared; four transfer addressing modes: Fixed address to fixed address, fixed address to block address, block address to fixed address, and block address to block address; flexible trigger mode: edge or level trigger. Single, block or burst block transfer mode: Each time a DMA operation is triggered, data of different sizes can be transferred as needed The four addressing modes of DMA are shown below: DMA controller module: 3 independent transmission channels: channel 0, channel 1 and channel 2. Each channel has a source address register, a destination address register, a transfer data length register, and a control register. Trigger requests for each channel can be allowed and disabled separately; configurable channel priority: priority decision module, the priority of the transmission channel can be adjusted, priority is determined for the channel with the trigger request, and the priority of which channel is determined. highest. The MSP430's DMA controller can be fixed priority and can also use cyclic priority. The program command control module, before each DMA channel starts to transmit, the CPU should program the relevant command and mode control to determine the type of DMA channel transmission; configurable transfer trigger: trigger source selection module, DMAREQ (software trigger) , TImer_ACCR2 output, TImer_BCCR2 output, I2C data reception ready, I2C data transmission ready, USART receive transmission data, DAC12 module DAC12IFG, ADC12 module ADC12IFGx, DMAxIFG, DMAE0 external trigger source. It also has trigger source expansion capabilities. DMA has six transmission modes: single word or single byte transmission; block transmission; burst block transmission; repeated single word or single byte transmission; repeated block transmission; repeated burst block transmission. The first three, DMAEN is automatically reset after the transfer is completed; the DMAEN bit needs to be reset when retransmitting to enable the DMA channel. The last three are in repeat mode. After one transfer is completed, DMAEN is not reset; when it is started again, data transfer can be started again. The six transfer modes are set by the DMADTx register: DMADTx Transfer Mode DescripTIon 000 Single transfer Each transfer requires a trigger. DMAEN is automaTIcally cleared when DMAxSZ transfers have Been made. 001 Block transfer A complete block is transferred with one trigger. DMAEN is automatically cleared at the end of the Block transfer. 010, 011 Burst-block transfer CPU activity is interleaved with a block transfer. DMAEN is automatically cleared at the end of the Burst-block transfer. 100 Repeated single transfer Each transfer requires a trigger. DMAEN remains Enabled. 101 Repeated block transfer A complete block is transferred with one trigger. DMAEN remains enabled. 110, 111 Repeated burst-block CPU activity is interleaved with a block transfer. Transfer DMAEN remains enabled. Single word or single byte transfer: The DMA channel is defined as a single word or single byte transfer mode, and each word or byte of the transfer is triggered by a signal trigger. Setting DMADTx=0 defines a single-word or single-byte transfer mode. The DMAEN bit is automatically cleared after the specified transfer is complete. If retransmission is required, the DMAEN must be reset. If DMADTx=4 is set to repeat single word or single byte transfer mode, the DMAEN bit remains set, with one transfer per trigger. The DMAxSZ register holds the number of transmitted units. If this register is 0, there is no transfer. The value of the DMAxSZ register is written to a temporary register before transfer, and DMAxSZ is subtracted after each operation. When DMAxSZ is reduced to zero, its corresponding temporary register re-sets the original value into DMAxSZ and the corresponding DMAIFG flag is set. Block transfer mode: In block transfer mode, one block of data can be transferred per trigger. Set DMADTx=1 to block transfer mode. After each data block is transferred, the DMAEN bit is automatically cleared. This bit will be reset before triggering the transfer of the next data block. Other transmission requests are ignored during the transmission of a block of data. Set DMADTx=5 to repeat block transfer mode. After a data block is transferred, the DMAEN bit remains set. After that, the new trigger can cause another block transfer. The DMAxSZ register holds the number of cells contained in the data block. DMASRCINCR and DMADSTINCR reflect changes in the destination address and source address during block transfer. During block transfer or repeated block transfer, the values ​​of the DMAxSA, DMAxDA, and DMAxSZ registers are written to the corresponding temporary registers. The temporary values ​​corresponding to the DMAxSA, DMAxDA registers are increased or decreased during block transfer, while DMAxSZ is transferred in blocks. During the process of counting down, it always reflects how many units of the current data block are not transferred. When DMAxSZ is reduced to 0, its corresponding temporary register re-sets the original value into DMAxSZ, and the corresponding DMAIFG is set. During block transfer, the CPU pauses and does not participate in the transfer of data. The data block requires 2 × MCLK × DMA x SZ clock cycles. When each data block is transferred, the CPU resumes execution in the state before the pause. Burst block transfer mode: This is similar to the block transfer mode except that each time 4 words or bytes are transferred, the DMA releases the internal bus, and the CPU runs 2 MCLK cycles; the CPU has 20% of the execution time during the transfer, and the block The transfer needs to wait until the DMA is completely transferred before the CPU can run. DMA trigger source: The trigger source of each channel is controlled by the DMAxTSELx bit. These bits must be set when the DMAEN bit is 0. Otherwise, unpredictable DMA trigger may occur. DMAxTSELx Operation 0000 DMAREQ bit (software trigger) 0001 TACCR2 CCIFG bit 0010 TBCCR2 CCIFG bit 0011 URXIFG0 (UART/SPI mode), USART0 data received (I2C mode) 0100 UTXIFG0 (UART/SPI mode), USART0 transmit ready (I2C mode) 0101 DAC12_0CTL DAC12IFG bit 0110 ADC12 ADC12IFGx bit 0111 TACCR0 CCIFG bit 1000 TBCCR0 CCIFG bit 1001 URXIFG1 bit 1010 UTXIFG1 bit 1011 Multiplier ready 1100 No action 1101 No action 1110 DMA0IFG bit triggers DMA channel 1 DMA1IFG bit triggers DMA channel 2 DMA2IFG bit triggers DMA channel 0 1111 External trigger DMAE0 In addition, the interrupt program of the MCU does not affect the DMA transfer. When the DMA transfer process, the MCU does not respond to all interrupts in the external NMI interrupt (the MN control bit ENNMI bit is 1 when responding to the NMI interrupt, otherwise it will not be processed); You must wait for the DMA data transfer to complete before running the system's interrupt handler. DMA interrupt: During data transfer, when DMAxSZ register value is reduced to 0, DMA sets DMAIFG, DMA interrupt and DAC12 module share interrupt vector. When using interrupt, software needs to judge which interrupt is specific. After the interrupt is responded, the DMAIFG will not be automatically reset. The DMAIFG bit must be cleared by software during use. The registers of the DMA are as follows: Register Short Form Register Type Address Initial State DMA control 0 DMACTL0 Read/write 0122h Reset with POR DMA control 1 DMACTL1 Read/write 0124h Reset with POR DMA channel 0 control DMA0CTL Read/write 01E0h Reset with POR DMA channel 0 source address DMA0SA Read/write 01E2h Unchanged DMA channel 0 destination address DMA0DA Read/write 01E4h Unchanged DMA channel 0 transfer size DMA0SZ Read/write 01E6h Unchanged DMA channel 1 control DMA1CTL Read/write 01E8h Reset with POR DMA channel 1 source address DMA1SA Read/write 01EAh Unchanged DMA channel 1 destination address DMA1DA Read/write 01ECh Unchanged DMA channel 1 transfer size DMA1SZ Read/write 01EEh Unchanged DMA channel 2 control DMA2CTL Read/write 01F0h Reset with POR DMA channel 2 source address DMA2SA Read/write 01F2h Unchanged DMA channel 2 destination address DMA2DA Read/write 01F4h Unchanged DMA channel 2 transfer size DMA2SZ Read/write 01F6h Unchanged Refer to the user guide provided by ti for details on each register. Damping and Absorption Capacitors

MKP capacitor

The products have a high share in China, and also used for INDUCTOTHERM,ELECTROTHERM,MEGATHERM,PILLAR,SUPERHEAT,ABP

, Mitsubishi electric, Fuji, the United States Yingda equipment and other

manufacturers of induction Furnace.

MKP Capacitor,MKP Capacitor 0.15UF,MKP Capacitor 20UF,MKP Capacitors 0.22UF YANGZHOU POSITIONING TECH CO., LTD. , https://www.cnchipmicro.com

How does the microcontroller expand the DMA function?

What is the DMA in the microcontroller?