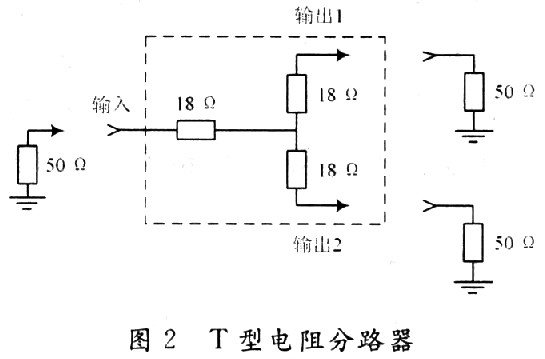

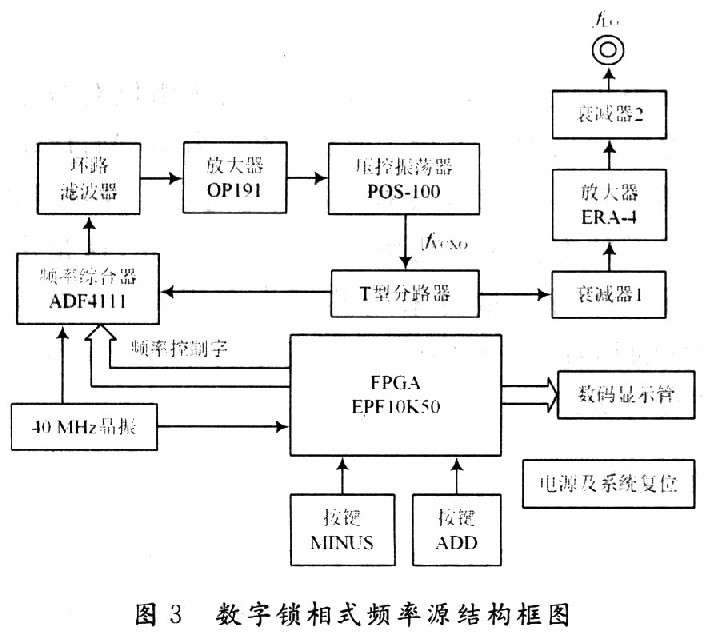

Frequency synthesis technology refers to a standard reference frequency with high stability and accuracy. After a series of processing, a large number of discrete signal frequency outputs with the same stability and accuracy are generated, and the frequency of the output signal can be controlled by digital signals. Change, its main application is to provide local oscillator for the intermediate frequency or RF signal of up / down conversion. There are three basic methods of frequency synthesis: direct frequency synthesis, phase-locked frequency synthesis, and direct digital frequency synthesis. The phase-locked frequency synthesizer is the most widely used frequency synthesizer nowadays. It has a wide output frequency range and good spurious suppression characteristics. In the short wave digital receiving system, the short wave signal received from the antenna end is mixed with the local oscillator signal to obtain a 70 MHz intermediate frequency, and then the intermediate frequency signal is band-pass sampled. The stability and accuracy of the local oscillator signal have an important and direct impact on system performance. This article uses frequency synthesis technology, using the frequency synthesizer ADF4111 of ADl company and FLEXlOKE series FPGA of Altera company to realize frequency stability, high precision, the range is 70 ~ 90 MHz, the step-by-step digital phase-locked frequency source local oscillator of 1 MHz. A phase-locked loop (PLL) is a loop control system based on phase negative feedback, as shown in Figure 1. A phase-locked loop consists of the following four parts: It uses the R frequency division of a high accuracy and stability crystal oscillator as the input reference frequency. The input reference frequency is used as the reference of the phase discriminator and compared with the output of the voltage controlled oscillator to produce a phase corresponding to two signals. Poor current pulse. The current pulse is integrated by the loop filter to generate a control voltage, and the high frequency components and noise are filtered out. This voltage drives the output frequency of the voltage controlled oscillator (VCO) to increase or decrease. When the loop is locked, the frequency difference between the input reference frequency and the N-frequency output of the voltage-controlled oscillator is zero, and the phase difference no longer changes with time. At this time, the control voltage is a fixed value, and the loop enters a locked state. When the input reference clock fREFIN and the output frequency of the voltage-controlled oscillator fVCXO are divided by R and N, the frequency and phase are the same, the output e (s) of the phase detector is O, and the loop will be Is locked. It can be derived from the equation e (s) = FREFIN / R-FVCXO / N. When e (s) = 0, fREFIN / R = FVCXO / N, that is, FVCXO = NFREIN / R. The phase-locked frequency synthesizer integrates R, N frequency division factor, phase discriminator, and charge pump in a single chip, which has a good suppression effect on phase noise and spurs, and is simple to debug. As a core component in systems such as communications, radar, telemetry and remote control, and electronic reconnaissance, it is one of the key factors to ensure the performance of the entire electronic system, so it is currently widely used in many fields such as television, instrumentation, and communication. According to the system requirements, the design indicators of the digital phase-locked frequency source are mainly: the output frequency is 70 ~ 90 MHz; the step interval is 1 MHz; the output power is 9 dBm. In order to meet these three main indicators, the design considers the design of the program and the selection of devices from the following three aspects. 2.1 Output frequency In order to obtain a high-precision frequency with an output range of 70 to 90 MHz, the high-performance phase-locked frequency synthesizer chip ADF4111 introduced by ADI is used in the design. The highest frequency of its RF feedback input is 1.2 GHz, which is a phase-locked loop The maximum available output frequency meets the requirements of the frequency output range of this design. The chip can be used in wireless radio frequency communication system base stations, wireless local area networks, mobile phones, and communication detection equipment. It is mainly composed of four parts: (1) Low-noise frequency discriminator (PFD). When using it, you need to configure the register. In addition to configuring the chip working mode, the register configuration is mainly to set the input clock division factor R and the VCXO input division ratio A, B, so that the two input clocks of the phase detector are equal. The relationship between the clock output by the VCXO and the input clock is: FVCXO = [(P & TImes; B) + A] FREFIN / R. Where: P is the prescaler factor; FREFIN and FVCXO are the input reference clock frequency and the output frequency of the voltage-controlled oscillator, respectively. The configuration of the register can adopt the method of FPGA control. FPGAs are more and more widely used because of their high integration, powerful functions, user programmable, and small size. In this design, the configuration of the register is also flexible and convenient. In the design, the FLEX series chip EPFlOK50EQC240-3 with the structure of 0.25μm CMOS ROM process specification of Altera is selected. The FLEX series chip is a medium density device, based on the lookup table structure, with high performance and low power consumption. FPGA program development is implemented by Altera's Quartus II software, and the ADF4111 register configuration program is written in AHDL hardware description language. The voltage-controlled oscillator that forms a phase-locked loop with the frequency synthesizer ADF4111 uses Mini-circuit POS-100, which is a voltage-controlled oscillator with excellent performance. Its tuning voltage range is 0 to 16 V, and the corresponding output frequency The range is 45 ~ 110 MHz, the voltage adjustment sensitivity is 4.2 ~ 4.8 MHz / V, and the typical value of the output power is 8.3 dBm. It is known from the voltage-frequency relationship that when the output frequency is 90 MHz, The corresponding input voltage is between 11.5 to 12 V. When the analog and digital power supply terminals of the ADF4111 are added with a 3.3 V voltage and the charge pump power supply terminal is added with a 5 V voltage, the charge pump output passes through the loop filter The maximum voltage is 5 V. If the 5 V voltage is not amplified, it obviously cannot drive the voltage controlled oscillator to generate a frequency of 90 MHz. For this reason, an amplifier needs to be added after the loop filter. OP191 is an AD company's amplifier with a power supply voltage of 2.7 to 12 V. It is mainly used in industrial control, telecommunications, remote sensing and other fields. The design is 12 V, which can make its output voltage up to 12 V, which can meet the tuning voltage input requirement of the voltage controlled oscillator output frequency of 90 MHz. 2.2 Frequency stepping The method to realize the frequency step is to change the register configuration value of the frequency synthesizer ADF411l, so as to adjust the output frequency of the voltage controlled oscillator to achieve the lock of the loop, and finally achieve the step of the output frequency of the voltage controlled oscillator. The stepping of the frequency should not only increase the VCO output frequency but also reduce it. Therefore, in the design, two buttons are used to initiate the increase and decrease of the instruction requirements, and the corresponding configuration of the ADF411l register configuration is realized by AHDL programming through FPGA. instruction. 2.3 Output power According to the signal flow, the output of the voltage-controlled oscillator POS-100 is divided into two channels: one channel is fed back to the ADF4111, and the other channel is used as the local oscillator output. At this time, the output of the voltage-controlled oscillator needs to be divided into two channels through a T-type network, where the T-type network is a resistance shunt, as shown in FIG. 2. It is widely used in a situation where one source needs to drive two loads, and its purpose is to perform impedance matching of the circuit. Three resistance values ​​of 18 Ω are commonly used in a Y-shape. If one of the loads is 50 Ω, it is equivalent to a T-type network with an attenuation of 6.3 dB. In the system, the working clock of FPGA and the input reference clock of the frequency synthesizer ADF4111 are provided by the 40 MHz TCXO clock of American WINTRON company. According to the digital phase-locked frequency source design scheme, the designed hardware structure is shown in Figure 3. (1) Receive the command of the button to increase or decrease the output frequency fVCXO; The design of the phase-locked loop is the key to ensure that the system can produce stable, high-precision local oscillator output. The local oscillator output from the voltage-controlled oscillator must pass through the attenuator and amplifier to ensure that the final local oscillator output power meets the requirements of the index. The following focuses on the circuit design of these two parts. 3. 1 PLL circuit design The phase-locked loop circuit design has two main parts: the ADF4111 design and the loop filter design. These two aspects are explained below. 3.1.1 ADF4111 design The four 24-bit control word registers in the ADF4111 are R frequency divider, N frequency divider, function register and initialization register. FPGA controls the phase-locked loop by setting the control words of these four control registers. ADF4111 input signals from outside include standard frequency source signal (40 MHz) and FPGA output control signal. After the standard frequency source signal is input to the ADF4111, the phase discrimination reference frequency is obtained through the 14-bit R frequency divider and sent to the phase detector. The control signal consists of a clock signal CLK, a data signal DATA and an enable signal LE. Under the control of CLK, the 24-bit data signal is input from the DATA signal terminal and temporarily stored in the 24-bit input register. After receiving LE, the previously input 24-bit data arrives at the corresponding latch according to the address bit. When the ADF4111 receives the output frequency from the feedback, it first obtains the feedback signal after frequency division through the prescaler scale factor P and the A and B frequency dividers, and then inputs it to the phase locker. Compared with the standard frequency source signal after frequency division in the phase discriminator, a low-frequency control signal is output to control the frequency of the external VCO so that it is locked at the stability of the reference frequency. The 40 MHz crystal is used as the standard frequency source signal in the design. In order to get the step of 1 MHz. The PFD input frequency of the ADF4111 is 1 MHz. So set the reference clock divider R to 40, and also set P = 8. Known by the relationship: FVCXO = [(P & TImes; B) + A] FREFIN / R, when FVCXO = 70 MHz, you can set counter A to 6 and counter B to 8, then the control words of the 4 control registers are set to R divider 6200AOH, N divider 200819H, function register 003092H, initialization register 003093H. When the button sends a command to increase or decrease the output frequency of the local oscillator, change the values ​​of counters A and B, and reload the control register of ADF411l, and finally realize the change of the output frequency of the local oscillator. Wuxi Juxingyao Trading Co., Ltd , https://www.juxingyao.com

1 Basic principles of PLL

(1) R frequency division factor, phase detector (Phase Detector), charge pump (Charge Pump).

(2) The loop filter is generally a low-pass filter. Its function is to filter the current output of the charge pump to drive the voltage-controlled oscillator, and its transmission factor is Z (s);

(3) The voltage controlled oscillator has a frequency sensitivity Kv / s;

(4) Feedback frequency division factor N.

2 Design scheme of digital phase-locked frequency source

(2) Charge Pump.

(3) Programmable preset frequency divider. It is mainly composed of three programmable counters: A counter (6 bits), B counter (13 bits), dual-mode preset frequency divider (P / (P + 1), P is the mode of the preset frequency divider), These three types of counters perform the N frequency division of the VCO output frequency to PFD to realize the operation of N = BP + A; the dual-mode preset frequency divider has four working modes: 8/9, 16/17, 32/33, 64/65;

(4) Reference frequency divider (R counter, 14 bits).

The typical value of the output power of the voltage-controlled oscillator POS-100 is 8.3 dBm. After passing through the T-shaped network, the signal power output as the local oscillator is 8.3-6.3 = 2 dBm. Obviously, the signal of 2 dBm needs to be amplified. Therefore, Mini-circuits' monolithic integrated circuit amplifier ERA-4 is used in the design. The frequency range of the signal it can amplify is 0 to 4 GHz, and the amplification gain for the 0 to 1 GHz signal is 14 dB. In order to ensure that the local oscillator input signal of ERA-4 is not saturated, in the design, the local oscillator signal of 2 dBm is input to ERA-4 after passing through a 4 dB attenuator. At this time, the power of the local oscillator signal output from ERA-4 is 2-4 + 14 = 12 dBm. Finally, in order to get a local oscillator output of 9 dBm, the signal output by ERA-4 needs to be attenuated by 3 dB. The design of the attenuator adopts a resistor-shaped matching network.

3 Digital phase-locked frequency source hardware design

As the logic control center of the system, the FLEXlOK50E chip integrates 50 000 gates and 2 880 logic elements (Logicelements) with a RAM capacity of 40 960 b. The main functions it completes are:

(2) Configure the frequency synthesizer ADF4111;

(3) Control the digital display tube to display the locked fVCXO value.