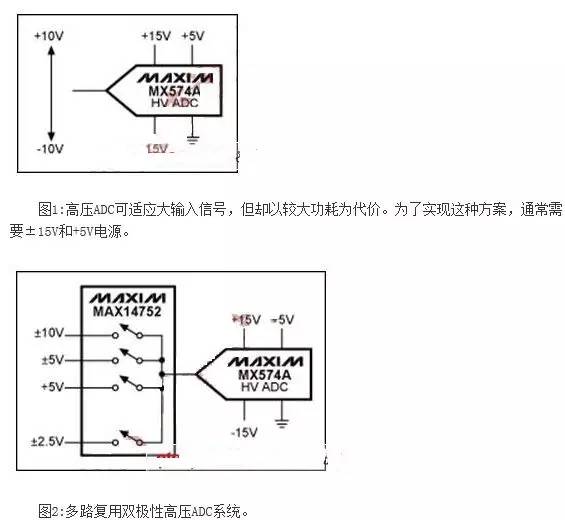

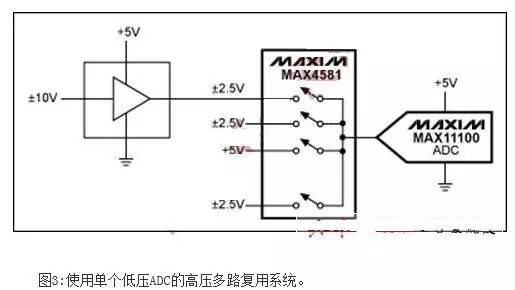

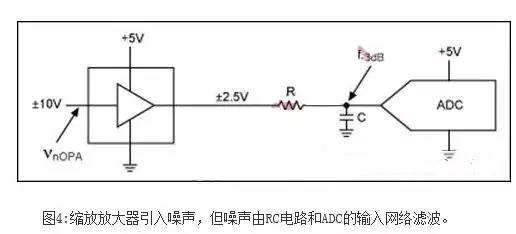

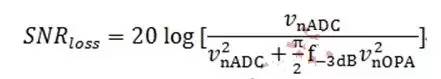

When designing with an analog-to-digital converter (ADC), it is easy to mistakenly believe that shrinking the input signal to meet the full-scale range of the ADC results in a significant reduction in signal-to-noise ratio (SNR). System designers who need to handle wide voltage swings are particularly concerned about this. In addition, low-voltage (5V or lower) ADCs are more diverse than higher-voltage-powered ADCs. Higher voltage supplies typically result in greater power consumption and more complex board layouts (for example, requiring more decoupling capacitors). This article will discuss the main factors that affect SNR loss (introduced by signal scaling), how to quantify it, and more importantly: how to minimize this impact. Many of the signals generated by sensors or systems are bipolar high voltage signals (such as the widely used ±10V signal). However, there are many simple ways to pass this signal through the ADC; various integrated high-voltage ADC solutions can also be used: this full-scale, large input signal can be processed without sacrificing SNR. These solutions require extremely high supply voltages to meet the input range requirements and their power consumption is considerable (Figure 1). These high voltage ADCs also reduce the range of signal conditioning (op amp) solutions. If the signal needs to be multiplexed with the high voltage and low voltage inputs, the system cost will increase significantly (Figure 2). The input amplifier can also be used to scale the signal to match the full-scale input range of the low-voltage ADC. This signal conditioning circuit can be connected to a multiplexed input so that all signals match the range of the ADC (Figure 3). When using an amplifier for signal voltage scaling, the noise is referenced to the amplifier input. At this point, there are two main sources of noise: the input reference noise of the amplifier itself, and the reduced input reference noise of the ADC. These two noise sources are combined in a quadratic manner. In addition, the amplifier's noise is filtered by the input bandwidth of the ADC and the anti-aliasing filter between the amplifier and the ADC input, see Figure 4. Figure 4: The scaling amplifier introduces noise, but the noise is filtered by the RC circuit and the input network of the ADC. The calculation formula for the system SNR (amplifier input) is: Where: VnADC is the input RMS noise of the ADC; VnOPA is the input reference noise of the amplifier (X times the input reference) = single pole -3dB frequency. Given the full-scale range of the ADC, the input reference noise of the ADC, and the scale factor of the amplifier, there are two variables that affect the target of SNR loss reduction: the cutoff frequency of the filter and the input reference noise of the amplifier. If the source has low frequency components, a filter can be designed to allow the amplifier to tolerate large input noise (higher input noise is usually associated with lower power and cost). If the ADC limits the bandwidth of the system, the amplifier needs to have low enough input reference noise to keep the SNR loss within an acceptable range. For example, given a ±10V input signal and a 5VP-P full-scale ADC with a SNR of 92dB, the scaling factor (the ratio of input to full-scale range) is 4. The ADC input reference noise in the datasheet is 44.4. nV RMS . Assuming that the cutoff frequency of the filter is 10 kHz and the input reference noise of the amplifier is 10 nV / (Hz) 1/2, the loss of SNR is: SNR (loss) = 0.035 dB. If there is no filter and the ADC bandwidth is assumed to be 10MHz, the required input reference noise becomes 0.3nV/(Hz) 1/2 in order to achieve the same SNR loss, which is very strict. For an ADC with the same bandwidth of 10MHz, if SNR(loss)=0.5dB is allowed, the noise requirement for the amplifier is 4nV/(Hz) 1/2, which is relatively easy to implement. Therefore, given the system bandwidth and tolerable SNR loss, adding a proportional amplifier to convert the high voltage signal to a full-scale low-voltage ADC would be a viable solution. This solution enables a cost-effective system when feeding multiple signals with different swings to a multiplexed low-voltage ADC. Half Cell Module,Solar Q Cells,Solar Pv Module,Monocrystalline Half Cell Module Jiangxi Huayang New Energy Co.,Ltd , https://www.huayangenergy.com

Design techniques to reduce ADC signal-to-noise ratio loss

Our half Cell Module, Solar Q Cells, Solar Pv Module, Monocrystalline Half Cell Module is hot sale. Half cell Solar Panels have Solar Cells that are cut in half, which improves the module`s performance and durability.