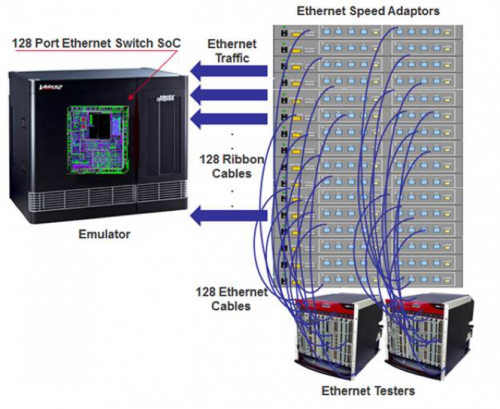

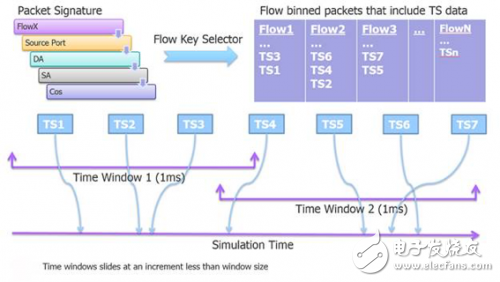

With the rapid development of the Internet of Things (IoT), network providers have also been greatly affected. After all, without the support of the network infrastructure, IoT will no longer exist. One of the consequences is a significant increase in the number of Ethernet ports in network devices. Today, Ethernet switches and routers have reached 256 ports (up to 1024 ports by the end of the year), and they can handle traffic up to 120 Gb/s. At the same time, the latency of network switching is continuing to decline, with the lowest latency dropping to 1 μs. All of these factors have made today's network switches and router chips the largest chip ever, reaching 500 million gates. Verifying such complex IC designs before tapeout is complete is a difficult task. Let's consider the SoC design with a 128-port Ethernet interface. Although it is possible to use HDL software emulation at the block level, it is impractical to use simulation traffic to verify the entire design of hundreds of millions of gates, and it will inevitably be eliminated. This is a major case of hardware simulation in the In-Circuit-EmulaTIon ICE mode. However, the ICE configuration requires an Ethernet tester for each port. Due to the speed mismatch, the tester and hardware emulator cannot be directly connected, and a rate adapter needs to be inserted between the two. For example, our 128-port design test setup requires 128 Ethernet testers and 128 Ethernet speed adapters, as well as all the wires that connect them (Figure 1). In addition to intricate cabling, potential hardware unreliability, and overall overhead, the entire setup can only support one user on-site debugging. Remote access is simply not possible because remotes require human intervention and different oath environments are configured for different users. The limitations of this kind of protocol to motivate the modeling environment have been around for a few years, so it is necessary to create a software-controlled environment for generating, transmitting, and analyzing Ethernet packets for hardware simulation. The mapped Ethernet SoC is tested. Through the software simulation method, 1,000 data packets can be verified every day, and the hardware simulation can handle more than 11 million. In this scenario, the Ethernet tester model runs on a Linux workstation connected to the hardware emulator. Based on the mature implementation IP, the model accurately reproduces the actual physical tester. This virtual tester includes an Ethernet Packet Generator and Monitor (EPGM) that can be configured with GMII, XGMII, XLGMII/CGMII, and CXGMII interfaces for 1G, 10G, 40G/100G, and 120G networks, respectively. An xRTL transaction processor is required for each supported MII port (Figure 2). Figure 1. A 128-port Ethernet switch using ICE authentication Multiple tester applications from multiple workstations can be combined to create multiple collaborative models to support large port count configurations. A collaborative model of each workstation is connected to the hardware emulator using a high speed link (HSL) card. The highly integrated transport mechanism optimizes clock performance maximization and is transparent to the test platform. Since the operation and debugging are parallel, the data plane hardware emulation traffic grows linearly with the number of ports. There are several other advantages to this approach. First, remote access can quickly reconfigure the virtual tester to perform various functions. Second, the workstation is a stable and reliable device that only accounts for a fraction of the cost of a complex Ethernet tester of equivalent functionality. More importantly, it can support multiple concurrent users and is especially useful when backing up large software development teams. Last but not least, the hardware emulation data center can be used as an enterprise-level hardware emulation resource. This method is also very suitable for the generation and monitoring of complex test scenarios. Use the interactive and batch mode TCL command interface to control all MACs and generate a wide variety of protocols and data. Each protocol can be mixed in percentages with different data lengths or random data lengths. The packet transmission arbitration strategy includes a variety of algorithms: WRR, DWRR, SO, and Random. Figure 2. VirtuaLAB Ethernet environment It also supports stress testing and error injection for complex switching topologies. Protocols and performance violations can be reported. Packets can be analyzed in interactive or batch mode to check packet statistics, Tx/Rx traces, metadata, timestamps, and everything in the line. One of the hallmarks of hardware emulation is its ability to perform complex performance analysis on large, complex systems. In some cases, millions of packets may be needed to cut the point of steady-state analysis in the current design. Take the measurement of the traffic bit rate of a mega-mega Ethernet switch. These measurements can be calculated using virtual Ethernet signature generation and packet timestamp (TS). Figure 3. With hardware emulation, measurements on each port can be completed in less than an hour. In a device software simulation with a large number of ports, each channel's measurement of each port can easily take a week. But with hardware simulation, the same measurement can be done in less than an hour. Conduction And Convection Dry Herb Vaporizers END GAME LABS,Conduction And Convection Dry Herb Vaporizers,Portable Dry Herb Vape,Dry Herb Vape Adapter END GAME LABS , https://www.eglvape.com