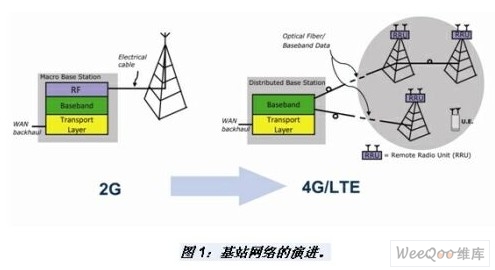

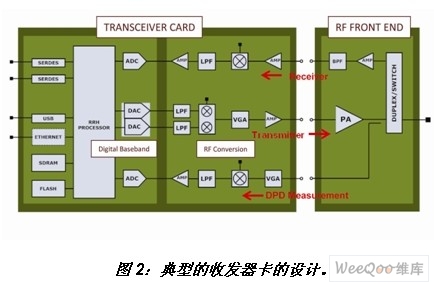

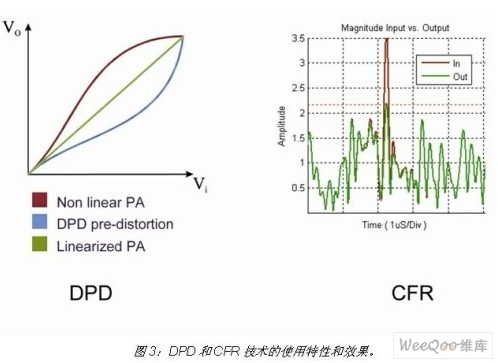

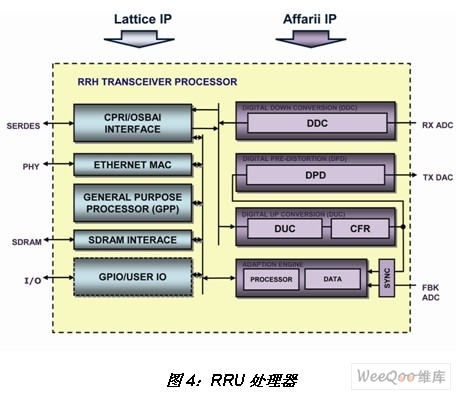

In addition to voice connections, digital cellular wireless networks (such as GSM and enhanced GSM-EDGE) can now provide higher data transmission rates, theoretically reaching the limit of 384kbps. Third-generation mobile networks (such as CDMA2000, WCDMA, TD-SCDMA) are currently being deployed worldwide. These systems provide video streaming, Internet browsing and other business services, using a technology called high-speed packet access (HSPA), which can theoretically provide a downlink rate of up to 14.4Mbps. Future infrastructure development (generally referred to as 4G systems) focuses on providing higher speeds and stronger functions at a very low cost. There are two technologies at the forefront of this development: 3GPP LTE for cellular / mobile technology (often abbreviated as LTE), and WiMAX for broadband wireless access. WiMAX has won early support for entering the market, but some handover problems between roaming and base stations still exist. Major cellular network operators support LTE as a technology of choice for the future. The two 4G standards use a common air interface standard based on OFDM (Orthogonal Frequency Division Modulation) and a MIMO antenna network. These advanced technologies enable the signal to recover from higher noise thresholds. The coexistence of these complex and sometimes competing technologies requires devices to support multiple air interface standards and more complex baseband processing. At the same time, these systems must provide sufficient flexibility to adapt to development plans and meet the requirements for increased bandwidth required in the future. In order to meet people's requirements for environmental protection, these devices also require a lower power budget. In the second-generation base station system, the macro base station is usually located under the antenna, and the RF power amplifier is close to the baseband and preamplifier. One development trend of the system is for distributed base stations. In these systems, baseband processing is independent of the RF power section. From an architectural perspective, moving from a macro base station to a distributed base station system (Figure 1) can greatly reduce system costs. In addition, the distance between the macro base station and the antenna must be within 150 meters, because there will be 50% RF power loss in the cable. The cost of updating and maintaining these devices is very high. A better solution is to use a distributed remote wireless network. The baseband is very far apart. A remote radio unit (RRU) with an RF power amplifier can be installed directly on the mast. The RRU unit can be linked to baseband via optical fiber and standard interfaces such as the Common Public Radio Interface (CPRI) or Open Base Station Architecture Initiative (OBSAI). FPGA in wireless infrastructure The characteristic of programmable technology is that it can follow the evolution of base station design, because the design usually starts before the specification is fully approved. Base stations require a large number of ASIC devices, and FPGAs are often used as interfaces and glue logic: they can quickly correct design errors or support the functions of specialized DSP devices. As wireless standards have evolved, the complexity of base stations has increased correspondingly. FPGAs are also constantly changing, and their performance and logic density have greatly increased. Engineers began to use FPGAs for more complex functions, such as digital down conversion (DDC) and digital up conversion (DUC). In response to these functions in base station design, the flexibility provided by FPGA means that FPGA is now an important element in the design process. LatTIceECP3 FPGA has many features, such as multiple embedded DSP blocks, embedded memory and SERDES functions. These functions are closely related to the evolving needs of wireless systems, so they are selected by design engineers. The flexibility of FPGAs allows engineers to quickly modify designs without having to wait for another ASIC to redesign the circuit board, thereby speeding time to market. Remote wireless unit / head The RRU function includes a transceiver card with digital signal processing, radio frequency conversion, power amplifier, duplexer and low noise amplifier (LNA) radio frequency front end. The design of the transceiver card is often broadband, with 80 to 90% component versatility between the wireless standard and the operating frequency band. A typical unit is shown in Figure 2. The reconfigurable nature of FPGAs allows software radio (SDR) technology to support multiple wireless standards, such as WCDMA, WiMAX, and LTE for general baseband. For MIMO antenna systems, the unit must provide a transmitter and receiver pair for each antenna. The next-generation network will operate at a much higher frequency than currently deployed networks, usually exceeding 2GHz, and in addition, it will need to provide a higher data transmission rate. The main RRU design issues are power consumption and the cost of RF power amplifiers. Large signal peak-to-average power ratio (PAPR) requires more power delivered by the power amplifier. Although this rarely happens, the design must implement this function, which will result in higher costs. RF transistors exhibit nonlinearity at high power, which will cause signal distortion and out-of-band emissions. The combined effect of the large signal peak-to-average power ratio and the nonlinearity of the 4G system may cause the power amplifier to only operate at 20-30% of its total output power, and the overall efficiency is only 10-15%. The operation of the GSM power amplifier can achieve 100% utilization and up to 70% efficiency. The solution to this problem is to pre-process this signal before the final power amplifier. In this way, the amplified RF signal has the best performance. Two methods can be used in this process: amplitude factor reduction (CFR) and digital predistortion (DPD). The working principle of crest factor reduction is to intelligently limit the maximum waveform amplitude of the power amplifier input, thus generating peak output power. This effectively reduces the PAPR of this signal, while maintaining the accuracy and spectral characteristics of the desired signal. In low power consumption or micro base stations, such as WiMAX or Picocell, it can be used without DPD. On the other hand, by applying a way to distort the input signal, DPD can linearize the power amplifier. This method takes into account the transmission characteristics of the power amplifier, and therefore invalidates any signal distortion, which is caused by the characteristics of the power amplifier. It is usually combined with CFR in high-power systems with RF output power greater than 1 ~ 2 watts. The characteristics and effects of these technologies are shown in Figure 3. Using CFR and DPD technologies in RRU allows system engineers to use lower cost power amplifiers than other technologies. Both methods require a lot of DSP processing functions to implement the necessary algorithms. The most important thing is that they also require a certain adaptability, because they need to adapt to any change in the transmission characteristics of the power amplifier, this change may occur in the case of temperature and time changes. The combination of remote wireless processors within RRU is one of the solutions to this problem. Traditionally, ASICs are widely used in the design of cellular base stations, but they have long design cycles, high fixed costs, and are not flexible, making them unsuitable for markets that are still evolving. For this problem, discrete DSP processors seem to be another solution, but analysis shows that they also have limitations in implementing multiple standard base stations. On the other hand, FPGA with embedded DSP unit, SerDes function and soft processor provides all functions in one reconfigurable chip. This device is ECP3 of Lattice Semiconductor. For any FPGA device with SERDES function, this FPGA has the industry's lowest power consumption and price. This series of products provides multi-protocol 3.2G SERDES, DDR1 / 2/3 memory interface, powerful DSP functions and high-density on-chip memory that comply with the XAUI jitter standard. Compared with FPGA with SERDES function, all these functions only need half power consumption and half price of competitive products. However, careful consideration must be given when choosing an FPGA to meet the physical and performance parameters of the system. Obtaining an IP core that implements key functions of RRU is critical to the overall system solution. As part of the IP Partner Program, Lattice is committed to this work together with Affarii, which has extensive experience in cellular wireless systems. The combination of LatTIceECP3 FPGA and Affarii's IP provides a flexible platform that can be combined to build all the IP modules required for RRU in the FPGA architecture. For sending and receiving, the function of the RRU processor is to multiplex and modulate this signal data to the RF carrier. Figure 4 shows the Lattice IP and the IP provided by Affarii. These blocks are distinguished by different colors. For different specific applications, the CFR configuration can be optimized. The simulation of the highest carrier configuration can determine the precise parameters. Standard system configurations are provided in the design tools and documentation. For users' own applications, users can also create custom configurations, use IP models and simulation environments with IP cores. Place the CFR IP in the LFE-70E FPGA for placement and routing, and the resource utilization is shown in Table 1a. It is the best method to determine the configuration of the DPD operation according to the characteristics of the power amplifier. The DPD core itself supports a diagnostic interface to provide on-site or test source data analysis. Using this tool, you can achieve the nonlinear complex characteristics of the amplifier, so you can decide the best configuration for the DPD. Because it measures real-time amplifier parameters, this process can also highlight the improvements that need to be made when designing the amplifier. Table 1b shows the resources required to place the DPD in LatTIce LFE-70EP for placement and routing. The Affarii IP includes not only CFR and DPD functions, but also DUC, DDC and matching engine functions, which is an important part of the base station structure. The main IP blocks provided by Lattice are CPRI and OBSAI. These are high-speed interfaces that use the embedded SERDES function in the FPGA to connect the remote baseband to the RRU. Ethernet MAC provides the function of monitoring and control system. Designers can also choose to use the LatTIceMico32 soft microprocessor for RRH general processing and control to reduce the number of components and save costs. The system can be completed with advanced memory interfaces and general-purpose I / O (GPIO) interfaces. Summary of this article FPGAs have now evolved into highly integrated devices that can include embedded ASIC-type functions and provide enhanced interface functions. The soft microprocessor function plus DSP processor and embedded memory means that the FPGA used in the base station design will provide a functional core with a reconfigurable chip. The advantages provided by programmable devices will enable products to enter the market faster and flexibly adapt to new standards and evolving cost-effective standards. Cummins 401-999KW Diesel Generator Cummins 401-999Kw Diesel Generator,Cummins Shanghai Genset,Cummins Shanghai Power Generator,999Kw Diesel Generator Shanghai Kosta Electric Co., Ltd. , https://www.ksdpower.com

Analysis of FPGA will be very important in 4G system

Analysis of FPGA will be very important in 4G system