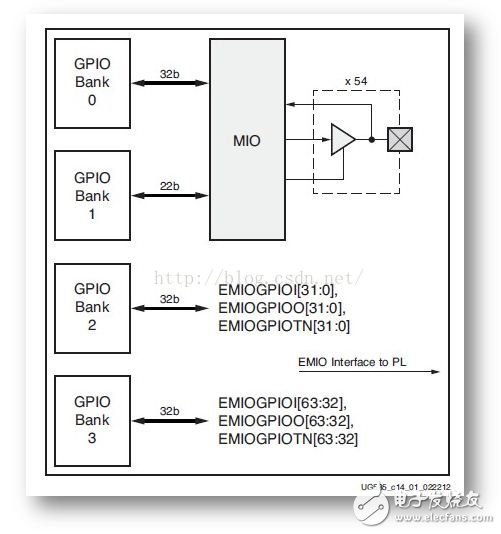

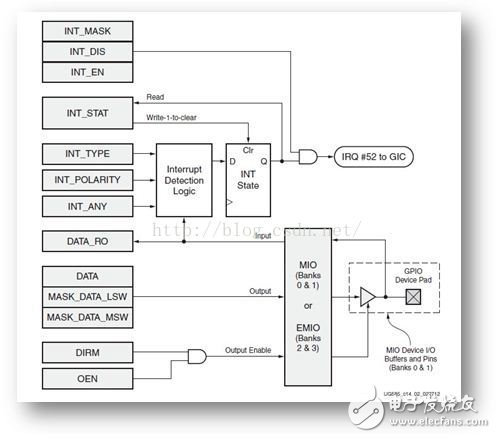

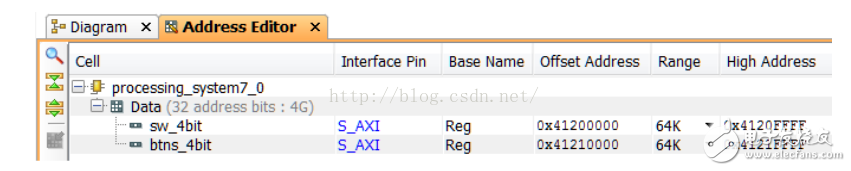

After learning zynq for a period of time, I was bluffed by zynq's GPIO when I came up. I really didn't figure out what's going on with zynq's GPIO. After a while, after a while, I slowly discovered that zynq has at least 3 types of GPIO. transfer. No wonder I think that every blog that introduces GPIO says something different. Let's first look at the three types of GPIO: MIO, EMIO, and AXI_GPIO. Among them, MIO and EMIO are GPIOs directly connected to the PS. And AXI_GPIO is hung on the GPIO on PS through AXI bus. Let's take a look at MIO and EMIO first: the structure of EMIO and MIO is shown below. Among them, MIO is distributed in BANK0 and BANK1, while EMIO is distributed in BANK2 and BANK3. Pay attention to a few items: First of all, the pins of MIO on zynq are fixed, while EMIO is extended through the PL part, so when using EMIO, you need to allocate pins in the constraint file, so when designing the program of EMIO, The bit file of the PL part needs to be generated and programmed into the FPGA. Secondly, it can be seen from the figure below that MIO occupies a total of 54 bits, while EMIO occupies 64 bits. The IO number occupied by MIO is 0-53. The IO number occupied by EMIO is 54-117. Furthermore, both EMIO and MIO belong to the IO on the PS and are directly operated by the PS. When calling the header file, just call #include “xgpiops.hâ€, and when calling AXI_GPIO, you need #include “xgpio.hâ€. Finally, after the bd file is designed, the system will automatically locate the path:. .\standalone_bsp_0\ps7_cortexa9_0\include generates xparameters.h file. We can Check the peripheral ID that we added during bd design in the xparameters.h file. For example, we have added EMIO, you can find the address and ID number of the IO. #define XPAR_PS7_GPIO_0_DEVICE_ID 0 #define XPAR_PS7_GPIO_0_BASEADDR 0xE000A000 #define XPAR_PS7_GPIO_0_HIGHADDR 0xE000AFFF Another example adds two AXI_GPIO, instantiated as BTNS_4BIT and SW_4BIT /* DefiniTIons for driver GPIO */ #define XPAR_XGPIO_NUM_INSTANCES 2 /* DefiniTIons for peripheral BTNS_4BIT */ #define XPAR_BTNS_4BIT_BASEADDR 0x41210000 #define XPAR_BTNS_4BIT_HIGHADDR 0x4121FFFF #define XPAR_BTNS_4BIT_DEVICE_ID 0 #define XPAR_BTNS_4BIT_INTERRUPT_PRESENT 0 #define XPAR_BTNS_4BIT_IS_DUAL 0 /* DefiniTIons for peripheral SW_4BIT */ #define XPAR_SW_4BIT_BASEADDR 0x41200000 #define XPAR_SW_4BIT_HIGHADDR 0x4120FFFF #define XPAR_SW_4BIT_DEVICE_ID 1 #define XPAR_SW_4BIT_INTERRUPT_PRESENT 0 #define XPAR_SW_4BIT_IS_DUAL 0 Take a look again, AXI_GPIO is equivalent to the IP core of GPIO. When we call, we occupy the corresponding AXI bus address space, as shown in the figure below, the occupied addresses are 0x41200000 and 0x41210000 Redundant Power Supply Series,Full Modular Redundant Power,800W Redundant Power Supplies,Redundant Server Power Supply 2000W Boluo Xurong Electronics Co., Ltd. , https://www.greenleaf-pc.com