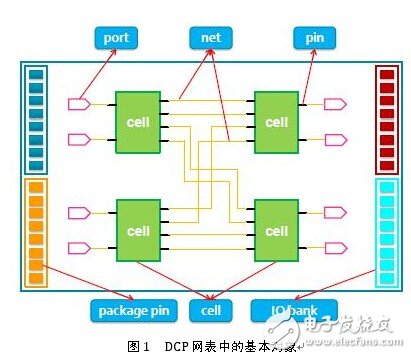

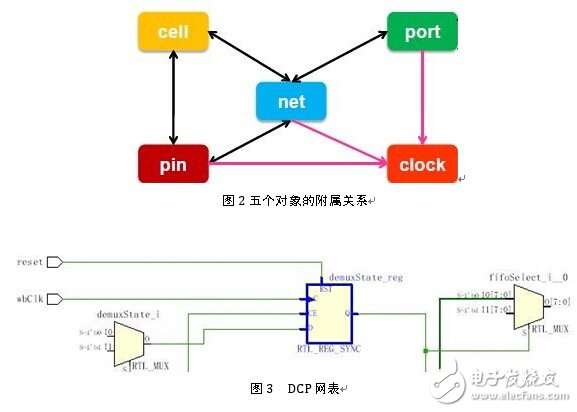

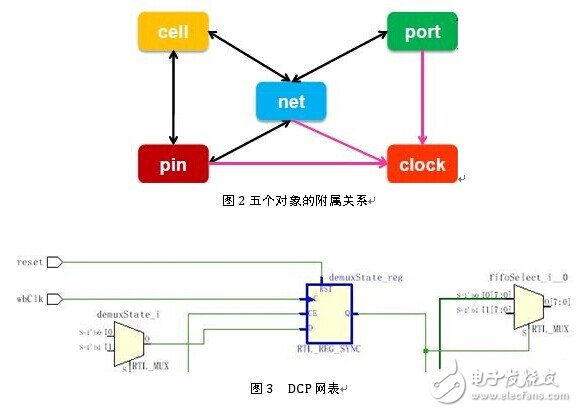

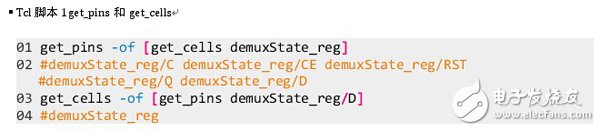

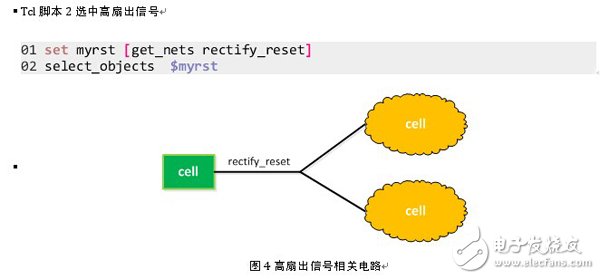

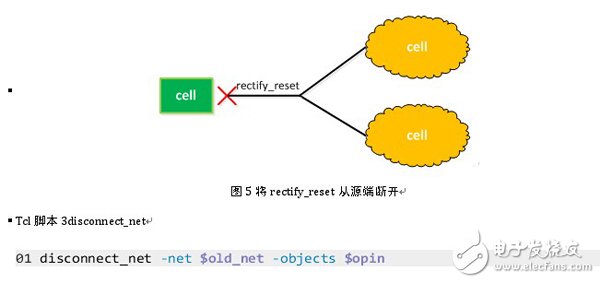

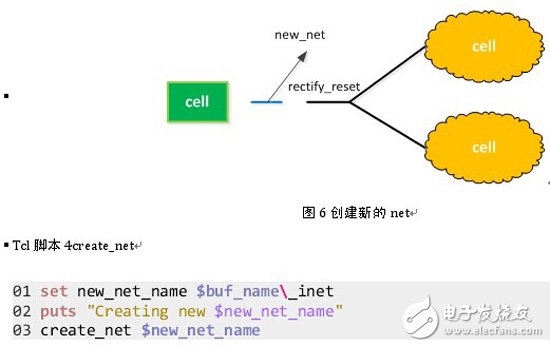

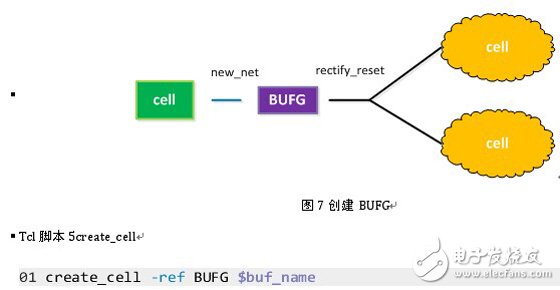

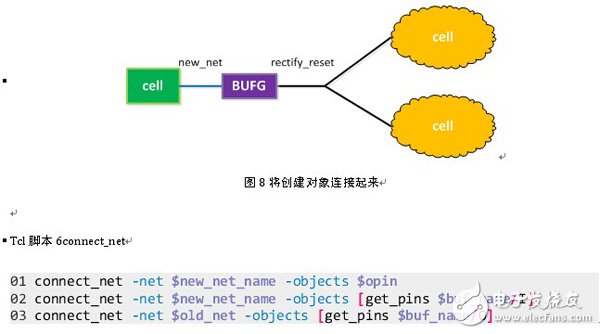

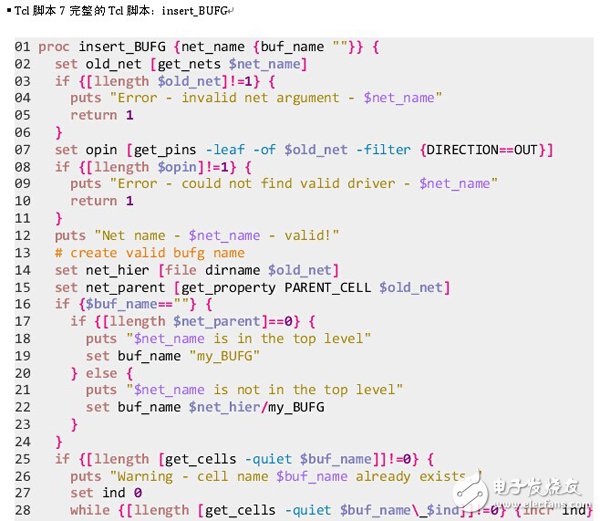

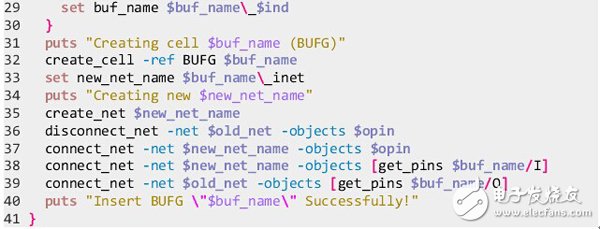

Under ISE, editing the integrated netlist is almost impossible, but it is possible under Vivado. Vivado's support for Tcl makes Tcl scripts useful in FPGA design. This article demonstrates how to use the Tcl script to edit a consolidated netlist under Vivado. Vivado supports traditional Tcl commands, and adds a lot of its own unique commands. These commands can be seen as further extensions to Tcl commands. Therefore, under Vivado, the graphical interface (GUI) mode has corresponding Tcl commands, which are usually displayed in the Tcl Console. On the contrary, many Tcl scripts can do things, but the GUI method can't handle them. This also shows the power of Tcl. This is the case for integrated netlist editing. When do I need to edit the integrated netlist? Usually it is necessary to make minor changes to the netlist, such as register copying or inserting BUFG into the high fanout net, inserting the pipeline register into the path with a larger logic level to improve the path delay, and changing the net to be tested. It should be noted that the significance of directly editing the netlist using Tcl is that it is possible to directly observe the edited effect without re-synthesizing to save the integrated time to determine whether such modification is needed. For example, a path with a large delay of the combined logic is inserted into the pipeline register. After Tcl editing, the timing report can be regenerated to observe how much the timing on the path is improved and whether the expected effect is achieved. If it is necessary to insert the pipeline register, it is still necessary to return to the HDL code for code modification. For another example, if you want to change the net to be tested, if a signal in the design needs to be led to the test port of the PCB, you can modify it directly in the netlist without going back to the HDL code to modify it. Here we first introduce the basic objects in the DCP netlist generated by Vivado: cell, port, net, pin, as shown in Figure 1, in addition to an important object clock. In Vivado, you can get them through the five Tcl commands get_cells, get_ports, get_nets, get_pins and get_clocks respectively. These five commands are the most basic and most commonly used Tcl commands in Vivado and will be used in subsequent netlist editing. The affiliation between these five objects is shown in Figure 2. Take the cell and pin as an example to illustrate the meaning of the arrow in the figure, as shown in the network table in Figure 3. Using the first line of the Tcl script 1 command, all the pins on the cell can be obtained by get_pins, and the return value is as shown in the second line. With the third line command, the cell where the pin is located can be obtained by get_cells, because the pin and the cell are in one-to-one correspondence. Here, an example of how to edit a netlist by inserting a BUFG into a high fanout signal is described. The engineering used is an example engineering cpu that comes with Vivado. Open the synthesized netlist file, find the high fanout signal recTIfy_reset through report_high_fanout_nets, and display the related circuit in schematic mode through Tcl script 2, which is shown in Figure 4. The first step: disconnect recTIfy_reset from the source, as shown in Figure 5, the corresponding Tcl script as shown in Tcl script 3. The second step: create a new net, as shown in Figure 6, the corresponding Tcl script as shown in Tcl script 4. The third step: create a new cell BUFG, as shown in Figure 7, the corresponding Tcl script as shown in Tcl script 5. Step 4: Connect the new net end to the source output pin, one end to the input pin of the BUFG; connect one end of the recTIfy_reset to the output pin of the BUFG, as shown in Figure 8, the corresponding Tcl script such as the Tcl script 6 Show. The full Tcl script is shown in Tcl script 7. The command insert_BUFG can be embedded in Vivado as a regular command. CIXI LANGUANG PHOTOELECTRIC TECHNOLOGY CO..LTD , https://www.cxblueray.com