Shanghai, China, September 11, 2017 — Xilinx, Arm, Cadence and TSMC today announced a collaboration to build the first inter-chip cache coherency (CCIX) based on the 7-nanometer FinFET process. The accelerator tests the chip and plans to deliver it in 2018. This test chip is designed to demonstrate at the silicon level that CCIX can support multi-core high-performance Arm CPUs and FPGA accelerators for consistent interconnection. About CCIX Demand for acceleration of applications in data centers is increasing due to power and space considerations, such as big data analytics, search, machine learning, 4G/5G wireless, in-memory data processing, video analytics, and network processing applications. , have benefited from an accelerator engine that can seamlessly move data across multiple system components. CCIX will support components to capture and process data anywhere, without the need for complex programming environments. CCIX will leverage existing server interconnect infrastructure to achieve higher bandwidth, lower latency, and cache-consistent access to shared memory. This will significantly increase the availability of accelerators and the overall performance and efficiency of the data center platform, reduce barriers to entry into existing server systems, and improve the total cost of ownership (TCO) of the acceleration system. About test chip The test chip with TSMC's 7nm process will be based on Arm's latest DynamIQ CPU and will use the CMN-600 to interconnect the on-chip bus and other base IP. To validate the complete subsystem, Cadence provides key I/O and memory subsystems including CCIX IP solutions (controllers and PHYs) and PCI Express 4.0/3.0 (PCIe 4/3) IP solutions (controllers) And PHY), DDR4 PHY, peripheral IP (such as I2C, SPI, and QSPI), and associated IP drivers. Cadence's verification and implementation tools will be used to build the test chip. The test chip can be connected to Xilinx 16nm Virtex UltraScale+ FPGAs via the CCIX chip-to-chip coherent interconnect protocol. Supply process The test chip will be released in the first quarter of 2018. The chip will be available in the second half of 2018. “We are accelerating computing through innovations in advanced technologies, so we are very excited about this collaboration. Our Virtex UltraScale+ HBM series uses the third generation of CoWoS technology, which we developed together with TSMC. Become the industry assembly standard for CCIX's HBM integration and cache coherency acceleration." -- Victor Peng, Chief Operating Officer , Xilinx "With the rapid development of artificial intelligence and big data, we have found that more and more applications are demanding continuous growth for heterogeneous computing. This test chip will not only prove that Arm's latest technology and consistent multi-chip accelerator can be extended to The data center demonstrates our commitment to the challenge of fast and easy access to data. This innovative collaboration for coherent memory is an important step toward a high-performance, high-efficiency data center platform." -- Noel Hurley, Vice President and General Manager, Infrastructure Division , Arm “By building a high-performance computing ecosystem with our partners, we will help customers rapidly deploy innovative new architectures on 7nm and other advanced nodes to serve growing data center applications. CCIX industry standards will help drive Next-generation interconnects provide the high-performance cache consistency required by the market." —— BabuMandava, Senior Vice President and General Manager of IP Department , Cadence “Artificial intelligence and deep learning will profoundly affect many industries, including healthcare, media and consumer electronics. TSMC's state-of-the-art 7nm FinFET process technology has the advantages of high performance and low power consumption to meet these markets for high performance computing. (HPC) different needs of the application." ——Dr. Hou Yongqing, Deputy General Manager of TSMC and Technology Platform

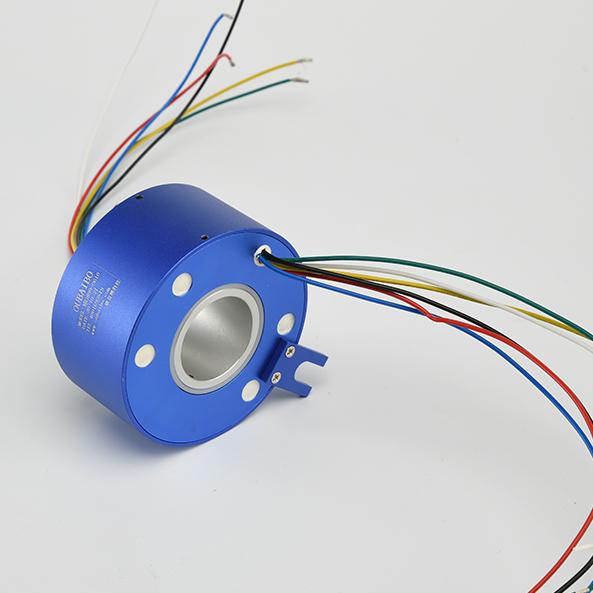

A through-bore slip ring is an electrical device that allows current to pass between two points in a rotating assembly without a physical connection. There is no break in the circuit. This is accomplished by passing the current through a rotating brush that contacts a stationary metal ring. The metal ring is mounted on the shaft of the assembly and provides a continuous path for the current.

It is an integrated circuit component that consists of two conducting rings that are separated by a gap or spacer. When the rings are brought into contact, current can flow between them and produce a rotational motion. Slip rings are used in various applications where high efficiency and low power consumption are essential, such as communication systems, motor control systems, and energy harvesting devices.

The through-bore design allows for rotation of the assembly while transmitting power or data. They are often used in applications where there is a need to rotate an object while keeping a power or data connection open, such as on a wind turbine or radar antenna.

The Oubaibo's through-bore slip ring is a newly designed product that has many advantages over other products on the market. It is small and lightweight, making it easy to install and use. The through-bore design also allows for a high degree of flexibility, making it ideal for use in difficult or tight spaces. Additionally, the Oubaibo through-bore slip ring is very efficient, providing a high degree of power transfer with minimal loss.

Through-Bore Slip Ring,Slip Ring Connector,Power Slip Ring,Slip Ring Assembly Dongguan Oubaibo Technology Co., Ltd. , https://www.sliproubo.com